# 半導體 IC 絕緣膜面臨技術革新

編輯室

半導體 IC 在邁入 65nm 電路線寬時,由於絕緣膜厚度在 4nm 以下時會產生「漏電流」現 象;而埋在配線間隙具防止漏電流功能的層間絕緣膜,也逐漸接近溦細化極限,線路愈來 愈細導致電訊號不容易通過,已經到了無法忽視的地步,因此各半導體公司紛紛研發新的 絕緣膜材料,設法跨越IC線路溦細化的極限。本文彙整高介電係數(High-K)材料絕緣膜及 低介電係數(Low-K)材料絕緣膜的研發現況與廠商動態,供業界參考。

#### 關鍵詞/Key Words

高介電係數(High-K)、低介電係數(Low-K)、半導體 IC (Semiconductor, IC)、絕緣膜 (Insulator)

# 前言

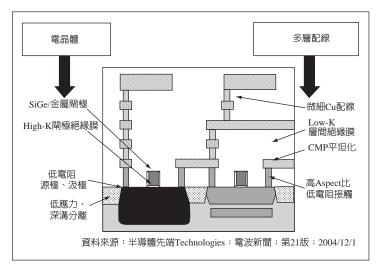

現在量產線寬 90nm IC 半導體係利 用氧化矽(SiO2)的閘極絕緣膜。隨著半 導體 IC 微細化的發展,絕緣膜即將面 臨材料的技術革新,尤其是當電路線寬 邁入 65nm 的下一代 IC 半導體,絕緣膜 厚度在4nm以下時,會產生量子力學中 所謂的「穿隧效應」,使絕緣膜的功能 無法發揮。換言之,閘極只有在施加電 壓時,電流才會通過絕緣膜流到下方的 電晶體,事實上,當絕緣膜厚度薄至約 2nm 以下時,膜中不純物會造成在未施 加電壓的情況下,絕緣膜上的電流仍在 流動的「漏電流」現象。另一種狀況是 受配線周圍絕緣膜(層間絕緣膜)電阻 的影響(如圖一),已經到了無法忽視 的地步,因此各半導體公司紛紛研發新 的絕緣膜材料,設法跨越 IC 半導體線 路微細化的極限。

# 閘極絕緣膜與漏電流現象

2005年起半導體業開始量產電路線 寬 90nm IC 半導體,一般預料 2007 年左 右,將開始量產線寬65nm的IC半導體。 2004年12月,在美國舉辦的半導體技

▲圖一 65nm 線寬之半導體製造必要的技術

術「國際電子元件會議」上,陸續發表 以量產化為目的之新材料,例如:

- 1.日本半導體先端技術 Selete,採用 「Hafnium Silicate」的高介電係數(High-K)材料,成功地試作出可以左右電晶 體性能的閘極絕緣膜。

- 2. 美國 IBM 也發表高介電係數絕緣膜與 金屬閘極組合而成的元件,成功地將 漏電流減低至過去的百萬分之一以下。

- 3.美國英代爾已確定將在電路線寬 45nm 以下的半導體元件導入高介電係數絕 緣膜。

左右半導體的最小單位-電晶體性 能的閘極絕緣膜材料正面臨轉換期,現 有的閘極絕緣膜使用的是二氧化矽,已 達材料極限,而半導體公司研發的對象 材料一開始為 HFSiO<sub>2</sub>,如今則有介電 係數更高的 Hafnium 與鋁的化合物 「HFAIO」,後者已成為下一代半導體 絕緣膜的候補材料。 High-K 材料的絕 緣膜係以原子層成長為1個分子大小的

厚度,相關的成膜設備需 求殷切。

#### 廠商動態

# 1.日本半導體先端技術 Selete

由日本10家半導體大 廠共同出資成立,與東京 Electron 公司共同確立下一 代紹小型電晶體製造用的 絶緣膜技術,在矽晶圓上 形成 High-K 絕緣膜的技

術,也就是在金屬氧化物電場效應 (MOSFET)上製作閘極時使用。

Selete 採用「Hafnium Silicate」的 High-K 材料成功地試作出左右電晶體性 能的閘極絶緣膜,即使只有 2~3nm 的薄 膜仍能維持其低漏電流的特性,結果雖 然實現了高集積度與節省電力,但卻造 成電晶體内部電子移動的速度下降,也 就是積體電路最重要的演算速度變慢。

Selete 尋求東京 Electron 公司的協 助,首先確認 High-K内的二氧化碳等 不純物成為汲極電流速度下降的原因, 由東京 Electron 公司開發「Teruformura」 熱處理設備,可以一面避免不純物的混 入,一面在晶圓上形成 High-K 膜。 Teruformura 可將 25 片晶圓固定在設備 内部的爐,連續進行下列工程:

- a.在晶圓表面形成二氧化矽的氧化膜; b.使用化學氣相沉積法在氧化膜上形成 High-K 膜;

- c.對膜加熱處理是讓材質安定,熱處理

時間為2小時,縮短為過去的六分之

#### 2.日本半導體 MIRAI 計劃

係由日本民間 25 家公司與產業技術總合研究所共同接受 NEDO 的委託,所執行的計劃叫做半導體 MIRAI 計劃,目的在開發電路線寬 45nm IC 半導體絕緣膜的成膜設備。 MIRAI 計劃於 2001年開始,2004年成功開發可對應 300mm晶圓的絕緣膜的成膜設備,由日立國際電氣公司於 2005年春開始供應,設備價格約 7 億日圓。

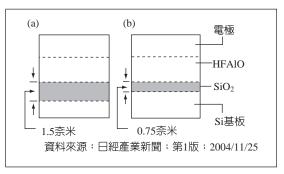

該設備使用 HFAIO 材料的 High-K 絕緣膜,閘極漏電流比使用 HFSiO 膜降 低約 2 位數。至於最令人擔心的 HFAIO 電子移動度低的弱點,則採用氮化(如 圖二)與氧化處理,也就是將厚度 2nm 左右的 HFAIO 薄膜與阿摩尼亞一起退 火(Annealing)氮化,之後再氧化,如此 處理順序還可以防止介電率低的氧化矽 層成長超過必要的厚度以上。電子移動 度為 260 伏特/秒.cm,為未退火前的約 2 倍,接近現在使用的氧化矽絕緣膜的 理論值(320 伏特/秒.cm),與 HFSiO 膜一樣良好。

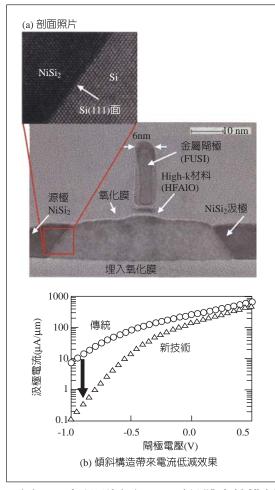

根據 FUSI 報告(本研究也是半導體 MIRAI 計劃成果之一),利用金屬閘極與 High-K 材料(HFAIO)形成完全空乏型 SOI (Silicon on Insulator)組成 MOS 電晶體,由於 MIRAI 開發超平坦技術接合了源極與汲極,實現了現階段最短只有 6nm 的閘極長度。試作 NMOS 電晶體的閘極電壓可以容許 5 位數的變化,擁有良好電晶體的特性。又為解決閘極長

▲圖二 (a)爲只有經氧化處理的絕緣膜; (b)爲經氮化、氧化處理的絕緣膜。結果(b) 的 SiO₂層比(a)薄,改善了電子移動度低的 弱點

度變短帶來源極與汲極間的漏電流變大的問題,在源極與汲極間使用鎳經砂化 (NiSi<sub>2</sub>)後將不純物注入 NiSi<sub>2</sub>中,不純物經 600°C 熱處理,則會在 NiSi<sub>2</sub>與 SOI 層的介面析出,而且已活化,因而可以防止不純物擴散至 SOI 層。這是因為源極與汲極接近通道(Channel)部份比過去傾斜(如圖三(a)),因而通道内側與源極與汲極的距離變大,漏電流就會減少(如圖三(b))。此外,注入離子使不純物析出的效果良好,加上具活化作用,注入離子只需 1 次(過去 3 次)即可抑制缺陷的發生,進而降低因缺陷引起的漏電流。

## 層間絕緣膜Low-K材料

積體電路内部配置了無數層的鋁配線藉以傳遞訊號,數年來,不斷地將電路微細化藉以實現高性能。事實上,不斷微細化的結果,會讓配線與配線太過於接近,因而增加訊號間彼此的干擾,導致 LSI 的運算速度無法再提昇,耗電量也跟著增加。解決之道,就是在配線

▲圖三 實現閘極長 6nm 電晶體之結構剖 面示意圖

工程採用銅取代鋁,層間絶緣膜則採用 低介電(Low-K)材料取代二氧化矽,這 些技術動向已正式運用且量產化。所搭 配平坦化的 CMP(化學機械研磨)設 備則必須是採低壓研磨。

#### 廠商動態

#### 1.日立製作所與日立化成工業

開發下一代半導體用絕緣膜,並在 2004年美國舊金山舉辦的國際電子元件

會議上發表。所開發的是低介電係數絕 緣膜,夾在LSI電路間以防止漏電流。 一般當絕緣膜的介電率下降,壽命也會 縮短,為此先闡明劣化的機制,構成絶 緣膜的有機與無機成分中,以有機成分 特別容易劣化,於是設法改變有機成分 中部份分子的結構,抑制劣化。傳統絕 緣膜的壽命大概為10年,新絕緣膜的 壽命是過去的100倍,像汽車等使用環 境條件嚴苛的都可以充分使用。

### 2.半導體 MIRAI 計劃

正在開發可望滿足微細化要求且具 可撓性的「Scalable 配線用絕緣膜技 術」,對Low-K絕緣材料的開發目標為 介電係數 1.5~2.0,以及具有可耐配線 製程的機械強度。總之, Scalable Low-K材料的開發,期待能持續使用到電路 線寬 45nm 世代。

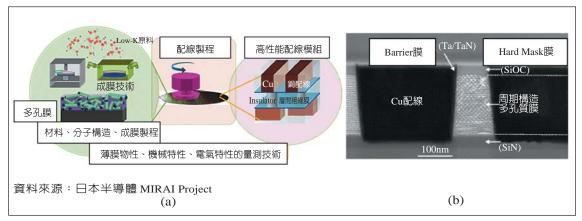

研究分兩階段進行,第一階段在開 發氧化矽材料中依設計導入奈米級空孔 的技術(如**圖四** $(a) \times (b)$ ); 第二階段 開發利用含有機材質的氧化矽氣相成長 技術,或利用電漿將兩種以上原料分子 結合的電漿共聚合技術(如**圖五**)。已 經完成可大幅提昇材料強度的氣體處理 新技術,而且已在300mm晶圓上形成 銅配線。此外, CMP技術是多孔 Low-K/Cu 配線工程的重要課題之一。

3.下一代半導體材料技術研究組合 (CASMAT)

對 Low-K 材料的開發已經進入實用 化階段,開發中的 Low-K 絕緣材為介電 係數 2.4 左右的塗佈型多孔質結構,已 經完成兩層配線及 Low-K 絶緣材,進入

(a)開發 Low-K 與銅配線膜組之基礎技術; (b)使用具週期性結構多孔質氧化 ▲圖四 矽膜

提高製程寬容度(Process Margin)的改良 階段。

### 4. 觸媒化成工業公司

為日揮的子公司,與富士通、富士 通研究所共同開發線寬 65nm LSI 多層 配線用低介電係數絶緣材料,亦可對應 於 45nm LSI 的需求。預計 2006 年在若 松工廠量產,產能500公升/月,量產 產品為「NCS (Nano Clustering Silica)」 的塗佈液,目前已經開始樣品試供。 5.Espec 公司

開發在350°C高溫下高精度量測 Low-K 膜絶緣特性評估系統,本系統的 特點: (1) 350°C下對專用 TEG的 VIA 配線間 Low-K 膜施加電壓,以測定其絶 緣破壞電壓;(2)在指定時間内以間隔 方式量測電流電壓特性(I-V特性);

▲圖五 利用電漿聚合之 Low-K 膜銅配線 晶圓(直徑 300mm)之1層銅配線剖面 SEM 照片 (彩色圖請見目錄頁)

(3)在電壓一定的條件下,量測任意溫 度(最多10點)下的漏電流。

#### 6.三菱電機公司

成功開發強度為其他絕緣膜 6 倍的 層間絕緣膜,其特點為使用稱為 "Borazine"的化合物,以及可以使用半 導體成膜設備,因此容易量產。