# 奈米世代DRAM技術發展趨勢

林正平

南亞科技公司 製程開發部

經理暨長庚大學電子系副教授

## 摘要

全球DRAM產業的製造與電路設計技術，在同業彼此競爭的壓力下突飛猛進。30年前，用8微米技術生產的千位元(kbit) DRAM的記憶細胞面積約是2400平方微米，隨著技術不斷進步，如今ITRS技術藍圖(International Technology Roadmap of Semiconductor)預估在2004年以90奈米技術生產的千兆位元(Gigabit) DRAM，其記憶細胞面積僅0.049平方微米，相當指甲般大小的晶片就可儲存超過一部大英百科全書資料，如此科技成就足以媲美人類登陸月球之壯舉。本文探討DRAM技術研發之現況，以及未來奈米世代主要關鍵技術之研發。

## 關鍵詞

奈米世代DRAM (Nanometer DRAM)；堆疊型電容(Stacked Capacitor)；深溝型電容(Deep Trench Capacitor)；高介電常數材料(High-k Dielectrics)；193 nm光學微影技術(193 nm Microlithography)；垂直式電晶體(Vertical Transistor)；DDRII

## 前言

動態隨機存取記憶體 (Dynamic Random Access Memory，以下簡稱DRAM) 因為兼具位元單位成本低與存取速度快等優點，三十年來一直是電腦中之主記憶體。世界各國半導體

大廠也莫不以DRAM作為研發更先進製造技術之利器。DRAM係於1970年代初期由美國開發成功並開始生產，惟在1980年代中期，日本挾其良率高及成本低等優勢，擊垮大部分美國DRAM廠，進而囊括近九成DRAM市場。1990年代則是韓國異軍突起，三

星電子公司於1983年才由64k開始切入DRAM產業，卻於1993年領先量產64M DRAM，且市佔率亦為全球第一。歸納其成功的因素主要為：1.政府鼎力扶植該項產業；2.大型企業支持與配合；3.卓越的研發人力；及4.低廉的勞工成本，故能於短短十年間超越美日的技術，成為全球DRAM公司之領導者。

我國於1993至1996年計有德碁、茂矽、世界先進、力晶、南亞科技及茂德等六家DRAM公司相繼成立。其中除世界先進公司技術由工研院電子所自行研發外，其餘公司都藉由美、日、歐等大廠移轉技術。最早係德碁與茂矽分別自德州儀器及日本沖電氣株式會社(Oki)移轉0.5微米16M DRAM技術，由於美、日、歐等大廠卓越的研發能力，以及我國優越人力素質與製造能力之最佳組合，奠定我

國DRAM產業於全球DRAM產業之舉足輕重地位。我國DRAM產值逐年增加，2001年佔全球市場16.9%，為全球第三大DRAM生產重鎮，製造技術也在2002年進入0.14微米世代，與市場領導廠商的量產時程差距不到半年。鑑於未來的奈米世代技術難度更高，研發經費更為天文數字，不免讓人產生觀望與質疑；惟2001年與2002年IEEE所舉辦的IEDM會議，全球DRAM大廠已紛紛公佈許多90奈米及70奈米世代的新技術（如表一），證明奈米世代DRAM技術已嶄露曙光，其未來發展亦樂觀可期。本文將摘錄該會議發表論文之相關技術內容，希望對國內DRAM公司發展奈米世代技術有所助益。

## DRAM技術演進及現況

1971年美國INTEL公司推出世界

表一 2002 ITRS深溝型DRAM技術藍圖

| Year of 1 <sup>st</sup> Product Shipment | 2003        | 2004        | 2005        | 2006                   | 2007                   |

|------------------------------------------|-------------|-------------|-------------|------------------------|------------------------|

| Technology Node                          | 100 nm      | 90 nm       | 80 nm       | 70 nm                  | 65 nm                  |

| Cell Size (μm <sup>2</sup> )             | 0.06        | 0.049       | 0.038       | 0.029                  | 0.025                  |

| Trench Depth (μm, at 35 fF)              | 8.2         | 6.9         | 6.9         | 6.8                    | 6.9                    |

| Aspect Ratio                             | 61          | 64          | 72          | 81                     | 88                     |

| Trench Structure                         | Bottled     | Bottled     | Bottled     | Bottled                | Bottled                |

| Trench Area Enhancement Factor           | 1.5         | 1.7         | 1.7         | 1.7                    | 1.7                    |

| Upper Electrode                          | Polysilicon | Polysilicon | Polysilicon | Metal/Poly-Si or Metal | Metal/Poly-Si or Metal |

| Dielectric Material                      | NO          | High-k      | High-k      | High-k                 | High-k                 |

| Bottom Electrode                         | Silicon     | Silicon     | Silicon     | Silicon                | Silicon                |

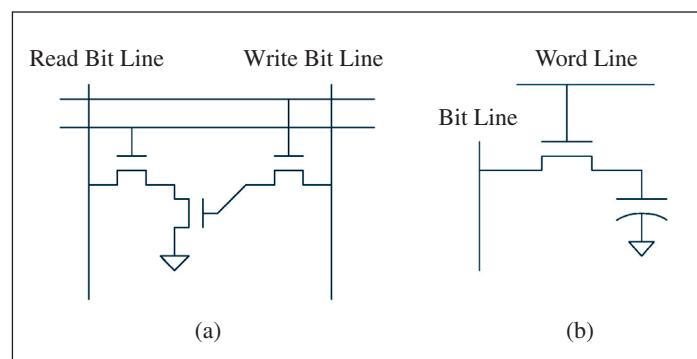

上第一顆 1k DRAM產品時，市場非常熱賣，且迅速取代電腦中之磁芯記憶體(Magnetic Core)。當時一個記憶細胞有三個電晶體、兩條Word Line和一至兩條Bit Line稱為3T Cell，而非目前DRAM通用的1T-1C Cell (如圖一)。所謂 1T-1C Cell係指記憶細胞僅有一個電晶體及一個電容，其主要設計概念係由 IBM工程師Dr. Robert H. Dennard於1966年發明，並由德州儀器公司於1973年發表4k DRAM產品中開始採用。1T-1C Cell的優點為記憶細胞面積遠較4T或6T的SRAM 記憶細胞為小；其缺點則為電容儲存的電荷會不斷流失，須於一段時間後補充電荷(Refresh)，其合理的電容值約為30fF/Cell，且不會隨著記憶細胞面積不斷微縮而改變，因此如何於有限的平面面積上增加電容的表面積，一直為DRAM研發技術之核心問題。

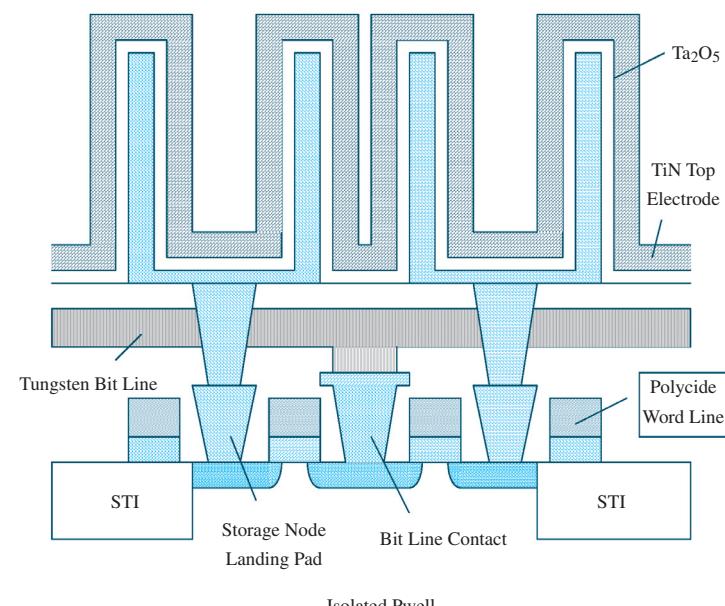

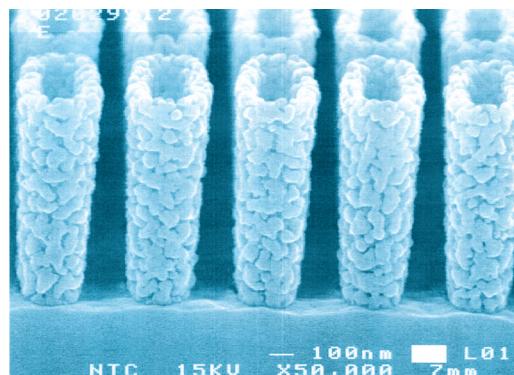

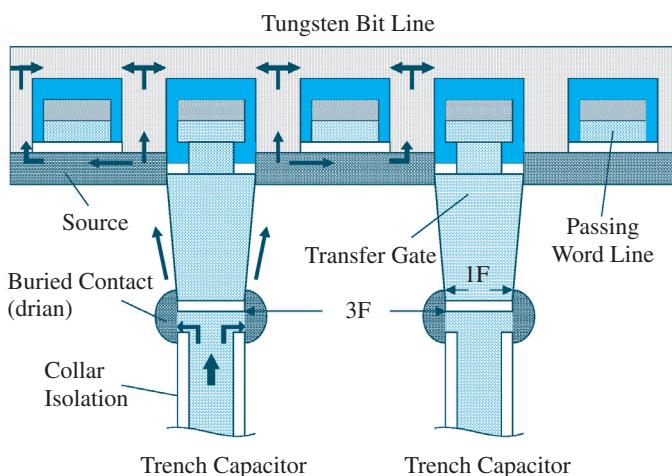

1980年代末期，4M產品 (0.8微米技術) 的記憶細胞開始往立體方面發展，其技術主要分為二種：其一為將電容疊在電晶體的上方，稱為堆疊型細胞(Stacked Cell)；另一為將電容埋在矽基底裡，置於電晶體的下方，稱為深溝型細胞(Deep Trench Cell)。此二種方式的DRAM技術，經過十多年的不斷創新及演變，已發展出各自最適合量產結構<sup>[1]</sup>。圖二為常見之堆疊型細胞的剖面示意圖，又稱Cylinder COB型。由多晶矽所形成的筒狀電極，除了筒柱的內外壁皆可貢獻表面積，還可藉

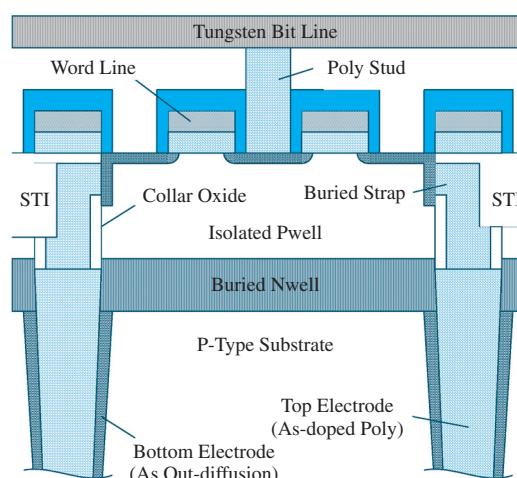

HSG(Hemi-Spherical Grain Polysilicon)之技巧，將表面粗糙化，使表面積再增加一倍，如圖三所示。COB係Capacitor Over Bit Line之縮寫，將電容置於Bit Line的上方，可避免挖過深之Bit Line接觸窗，且電容避開接觸窗亦可增加一些面積。圖四是深溝型細胞的剖面示意圖，又稱BEST Cell (Buried

▲圖一 DRAM記憶細胞電路比較(a) 3T Cell and (b)1T-1C Cell

▲圖二 堆疊型記憶細胞剖面示意圖

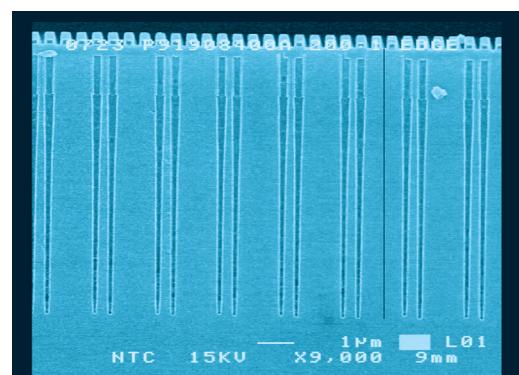

Strap Trench)由 IBM、西門子和東芝等公司共同研發<sup>[2,3]</sup>，其特點為電荷儲存在深溝內的多晶矽中，如此可避免鄰近兩根深溝電容間之漏電流。另電晶體的汲極與深溝內的多晶矽靠埋接窗(Buried Strap)連接之方式，為最省佈局面積之作法，惟為避免埋接窗對電晶體特性之影響，深溝內多晶矽多以砷摻雜(Doping)，採其擴散常數較低的優點。圖五為深溝型電容器之SEM放大

▲圖三 堆疊型筒狀電容器使用HSG製程的SEM照片

▲圖四 深溝型記憶細胞之剖面示意圖

圖。以上兩種電容的作法各有優缺點，總體而言，深溝型之優點為電晶體元件不受電容器高溫製程步驟之影響、特性較佳且晶片表面平坦，易於與邏輯製程結合發展成為單晶片系統產品(System on a Chip, SoC)。反之，堆疊型之優點為電容器可不受電晶體高溫製程步驟之影響，較易採用高介電常數材料來增加電容，大部分高介電常數材料都無法忍受800°C以上的高溫。

除了製造技術之進步，另值得一提為電路架構之改變。從64M開始為同步DRAM (Synchronous DRAM, SDRAM)的世代，亦為DRAM產業發展史之重要里程碑。由於DRAM與CPU時脈同步，所以CPU可一次下連串的讀寫指令(Pipelined Command)予DRAM，每一個指令都依時脈緊密的連結，有些I/O介面電路的動作，甚至可與記憶陣列(Memory Array)存取資料之動作同步進行，故可節省許多等待

▲圖五 深溝型電容器掃描式電子顯微鏡照片

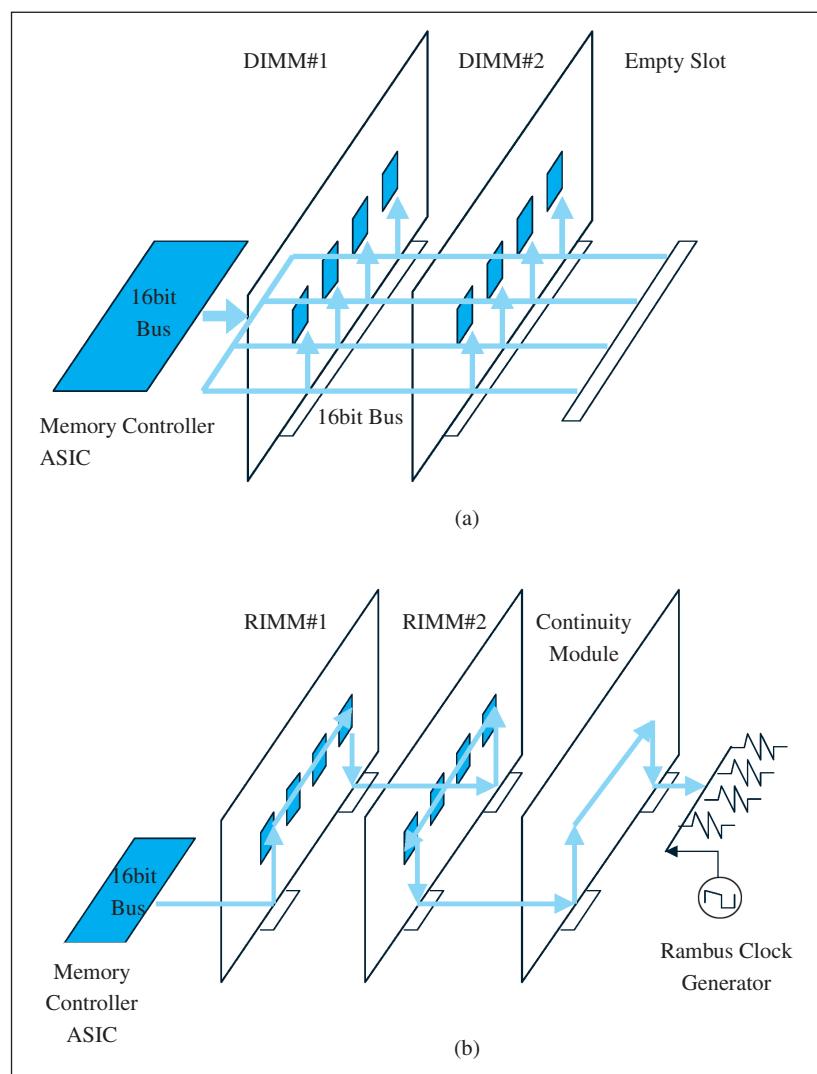

時間。所以資料之讀取時間可以縮短至7ns，與大部分非同步DRAM約60ns的資料讀取之時間相比，已有長足的進步。近年來，為因應高速CPU對DRAM資料傳輸頻寬之需求，亦發展出不同新型DRAM設計架構，其中最受市場歡迎的有倍速資料存取( Double Data Rate, DDR)及Rambus兩種。DDR

DRAM係改善SDRAM的資料進出介面電路，允許資料於時脈波的上緣(Rising Clock Edge)和下緣(Falling Clock Edge)都能進行傳輸動作，故資料傳輸頻寬能加倍。目前最快256M產品的輸出頻率為400MHz。Rambus DRAM則採用類似通信網路的介面電路架構，其資料通道是以傳輸線(Transmission Line)的方式處理，且加上DDR功能，所以能有絕佳的頻寬，若以400MHz輸入時脈和16bit資料

排線來計算，最高頻寬可達1.6 G bytes。此兩種規格DRAM各有其優缺點，市場上亦處於競爭狀態，圖六為上述兩種規格DRAM於電腦記憶系統中配置的比較示意圖。由於DDR的製造及測試成本較低，與SDRAM系統相容性高，故在系統廠商間的接受度較高，市場上佔有優勢。

▲圖六 DRAM在電腦記憶系統中之配置圖(a)DDR及(b)Rambus

## 奈米世代DRAM關鍵技術

### 一、193奈米光學微影技術

光學微影技術為積體電路微縮工程之火車頭，在文獻的討論中，許多人預期DRAM產業應該是在0.11微米世代，開始引用ArF準分子雷射光源的193奈米光學微影技術，惟事實上，在三星發表的論文中，90奈米才論及改用ArF光源，不似邏輯專工製程從0.13微米製程就已使用。DRAM製造需嚴格控管成本，設備機台的汰換通常能免則免，更遑論昂貴的掃瞄步進機之汰換，所以祇能不斷改善光罩技術來取代掃瞄步進機之汰換。且邏輯專工生產為少量多樣的產品，使用昂貴的光罩並不划算。一般來說，ArF光源的光阻(Photoresist)尚未十分成熟，其抗蝕刻性及附著性有待加強，且光阻厚度相當薄，故須仰賴硬罩幕蝕刻(Hardmask Etch)技術。就光罩技術而言，趨勢是從目前的低穿透率相位移光罩(Phase Shift Mask, PSM)走向高穿透率，如此能獲取較清晰的影像對比。此外Scattering Bar形式的光學鄰近效應修正(Optical Proximity Correction, OPC)、加強型偏軸照明(例如Dipole Type Off Axis Illumination)及二次曝光等技巧都將被廣泛採用。

### 二、高介電常數材料

90奈米以下技術若繼續用3D立體結構來增加電容，不管深溝型或是堆疊型技術將面臨極大挑戰，不是深度不夠，就是容易倒塌，所以高介電常數材料自然成為未來技術研發的重點。在0.18微米世代以前的技術，常用的電容器絕緣材料為氮化矽( $\text{Si}_3\text{N}_4$ ,  $\epsilon_r = 7$ )，而文獻中建議的高介電常數材料則有 $\text{Al}_2\text{O}_3$ ( $\epsilon_r \sim 9$ )， $\text{Ta}_2\text{O}_5$ ( $\epsilon_r \sim 25$ )， $\text{HfO}_2$ ( $\epsilon_r \sim 28$ )和 $\text{BaSrTiO}_3$ (BST,  $\epsilon_r > 320$ )等。就堆疊型技術而言， $\text{Ta}_2\text{O}_5$ 經過15年不斷研發，終於成為0.13微米世代的主流量產技術。而三星公司論文所公佈90奈米技術則是在MIS (Metal Insulator Silicon)結構之電容器上，採用 $\text{Al}_2\text{O}_3/\text{HfO}_2$ 雙層式絕緣體<sup>[4]</sup>。 $\text{Ta}_2\text{O}_5$ 在MIM結構介電常數雖可達50，但在整個產品的製程整合方面與BST一樣都未達成熟階段。至於深溝技術方面，德國英飛凌公司則是連續兩年在IEDM會發表論文，看好 $\text{Al}_2\text{O}_3$ 在未來深溝型DRAM的運用，主要係因 $\text{Al}_2\text{O}_3$ 是前述高介電常數材料中唯一可耐溫超過900°C以上，且其漏電流狀況與 $\text{SiO}_2$ 相近，但比 $\text{Si}_3\text{N}_4$ 為佳<sup>[5]</sup>。 $\text{Al}_2\text{O}_3$ 的薄膜厚度約4.5奈米，須利用原子層沈積的方式(Atomic Layer Deposition, ALD)均勻鍍在深達7微米深溝內。

英飛凌甚至嘗試把HSG技術與 $\text{Al}_2\text{O}_3$ 搭配使用，從該公司發表的論文

分析， $\text{Al}_2\text{O}_3$ 搭配HSG已能滿足90奈米世代的電容和漏電流需求，惟在70奈米以下技術，則仍需 MIS結構及更新高介電常數材料。

### 三、垂直式記憶細胞電晶體

DRAM記憶細胞電晶體(Cell Transistor)之元件設計與一般邏輯元件差異頗大，雖其導通電流祇需  $0.03\text{ mA}/\text{Cell}$ ，其漏電流則須滿足最嚴格的要求（小於  $1\text{fA}/\text{Cell}$ ）。在元件微縮產生短通道漏電流(Subthreshold Leakage)時，許多在邏輯元件用來克服短通道效應的技術都無法採用，主要係因這些技術都會惡化源汲極接面漏電流(Source/ Drain Junction Leakage)。前幾年，IBM公司提出垂直式電晶體的概念，將電晶體做在深溝內，並疊在電容器上方，此時電流是上下導通，而不是左右導通，如此一來，通道的長度不再與平面尺寸的微縮有直接相關，即使在100奈米世代，通道長度仍有0.2微米以上。但其主要問題為導通電流太小，因此IBM與英飛凌二家公司在2001年IEDM會中又提出雙通道垂直式電晶體的結構，如圖七所示<sup>[6]</sup>。惟此作法仍面臨製程過於複雜的問題，且因鄰近記憶細

胞的埋接窗相當接近，能否微縮到90奈米以下，尤有待進一步分析。至於堆疊技術方面，則是持續平面電晶體的微縮，三星公司在2002年IEDM所發表論文，則提出許多利用局部通道摻雜(Local Channel Doping)，以抑制短通道效應，但同時又不惡化源汲極接面漏電流的方法<sup>[4]</sup>。

### 四、DDR II電路規格誕生

DDR與Rambus DRAM所引發之高速DRAM戰爭，似乎僅是序幕而已，因隨著CPU運算頻率的快速增加，DRAM與CPU間之資料傳輸障礙日益嚴重，未來更高速DRAM的介面電路規格之爭仍暗潮洶湧。在新架構方面，NEC提出了虛擬通道(Virtual Channel)的概念，藉由on-chip SRAM快取記憶體減少DRAM Array存取次

▲圖七 雙通道垂直式電晶體之記憶細胞剖面圖

數；在電路規格方面，JEDEC也在2002年公布DDRII部分規格，讓整個電腦資訊產業對未來DRAM產品開發的方向更為明確。DDRII每次讀取資料固定為2個Clock Cycle，相較於DDR的最少一個Clock Cycle的規定，將使DRAM Array的資料存取擁有較充裕時間，且採用Micro-BGA封裝，訊號品質亦較佳。

未來週邊介面電路的電源規劃為1.8伏，以符合省電的趨勢，但這同時也對DRAM週邊介面電路元件的速度之要求更為嚴格。DDRII仍有許多規格尚需分析探討，這其中包括是否引進前述的on-chip SRAM快取記憶體概念。另外值得一提的是，當電路操作頻率超過400MHz時，DRAM封裝測試產業可能將面臨測試設備需全面升級的壓力。

### 結語

面對即將來臨的DRAM奈米世代，研發著重之關鍵技術主要可分為下列四項：

1. 193 nm光學微影技術和高穿透率型PSM光罩技術

2. 高介電常數材料製程整合及ALD薄膜沉積技術

3. 垂直式記憶細胞電晶體

4. DDRII以及更新的介面電路架構

就電容技術而言，深溝和堆疊兩大陣營仍是壁壘分明，誰能在奈米世

代勝出端賴研發能力及時效，因此同業間之合縱連橫方興未艾，例如去年南亞科技與德國英飛凌結盟；力晶則與日本爾必達(Elpida)結盟。值得慶幸的是我國DRAM產業同時擁有先進的深溝與堆疊型技術及全球最多的12吋廠，只要能持續維持製造技術之優勢，並在技術研發創新迎頭趕上，必可抵抗國際大廠的夾擊及擺脫大陸未來幾年可能帶來的威脅，在這場DRAM技術的接力賽中成功接棒成為新的領導者。

### 參考文獻

1. Nicky C. C. Lu, "Advanced Cell Structures for Dynamic RAMs," IEEE Circuits and Devices Magazine, pp. 27-36, 1989.

2. E. Adler et. al, "The Evolution of IBM CMOS DRAM Technology," IBM Journal of Research and Development," Volume 39, No. 12, 1995

3. L. Nesbit et al, "A  $0.6\mu\text{m}^2$  256MB Trench DRAM Cell with Self-Aligned Buried Strap (BEST)," IEDM, 1993

4. Y. K. Park et. al, "Highly Manufacturable 90 nm DRAM Technology," IEDM, 2002.

5. H. Seidl et. al, "A Fully Integrated  $\text{Al}_2\text{O}_3$  Trench Capacitor DRAM for sub-100 nm Technology," IEDM, 2002

6. R. Weis, "A highly Cost Efficient 8F<sup>2</sup> DRAM Cell with a Double Gate Vertical Transistor Device for 100 nm and Beyond," IEDM, 2001