# 金凸塊技術

# 與晶圓封裝的應用

黃祿珍 頎邦科技股份有限公司 工程部 副總經理

凸塊(Bump)技術在半導體封裝的應用有愈來愈多的趨勢,

其實凸塊技術的發展已有將近30年的歷史,

從最早期的金凸塊的應用及錫鉛凸塊的應用迄今,沒有多大的改變。

近幾年來凸塊技術會再有如此熱烈的反應,主要是市場面的擴大,

例如LCD市場的擴大帶動TAB or TCP 產品需求增加,

而以金凸塊為接合點的TCP封裝技術服務相對的市場就增加。

而覆晶(Flip-chip)結合技術需求增加,

也帶動了錫鉛凸塊製程的需求,

因為凸塊種類繁多,以下僅針對金凸塊做一技術簡介及產品應用。

# 金凸塊的產品應用

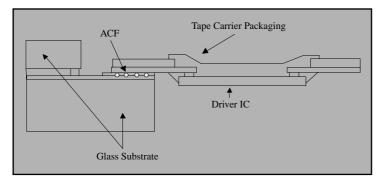

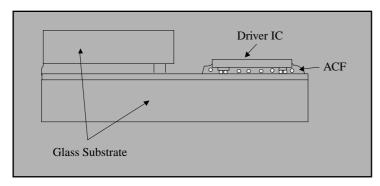

金凸塊 (Gold Bump) 的產品應用主要是在LCD產業的IC元件結合,比較有代表性的為 Tape Carrier Packaging (TCP), Chip On Glass (COG)如圖一所示,在TCP的IC元件結合中,外引腳Outer Lead Bonding (OLB)是將TCP結

合至LCD的玻璃基板上,而內引腳 Inner Lead Bonding (ILB) 和IC上的金凸塊相互結合,這是目前在大面積LCD上所用的IC元件結合技術,至於小面積的LCD基板上IC結合技術主要為Chip On Board (COB)及較先進的Chip On Glass。COG的結合技術是將控制IC直接以覆晶的方式結合至玻璃基板上,如圖二所示,控制IC的結合點是以金凸塊與異方性導電膜的金

圖一 The structure of Tape Carrier Packaging and Glass Substrate

圖一 Chip on Glass assembly and its structure

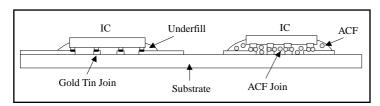

圖三 COF的元件結合方式

屬顆粒與玻璃基板上的線路互相連接, 形成控制迴路。

COG的結合技術應用在較小面積的玻璃基板,理由是產品單價及製造成本為考量因素。因為此項製程將IC以異方性導電膜反轉結合在玻璃基板上,異方性導電膜的重工性(Rework)並不好,且易造成基板及IC的損傷,所以在高單價大面積的LCD基板上大多有10 20個控制IC在LCD上,若因其中一個不良而且不能重工(Rework or Repair),造成的損失則非常可觀,再加上已既有的產品結構,並不是想改就可改,除非有重大的價格及技術因素,要不然大面積的

LCD面板和IC的結合,還會是以TCP為一 主流技術,而COG則會漸漸取代目前的 COB的IC結合方式,因為其方便的結合 方式可能減化製程 ,讓小型的模組更容 易組裝及生產。

COF(Chip on Film)是近來比較受到注意的元件結合技術之一,其結合方式是截取TCP及COG的各項優點。TCP是以軟性材料當基板,而COG是以覆晶的方式結合,所以COF可以是軟性基板再加上覆晶結合方式的組合,軟性基板的供應商很多,而且價格便宜,不像TCP的Tape供應商只有那幾家,價格也居高不下,在封裝產業使用自然不普遍。例如圖三所示,其結合點是以金凸塊為結合材料,當然其結合方式而引出不同種類的COF。未來何種會成主流,則依市場、價格及量產性而定了。

# 金凸塊的製程

金凸塊的製程流程非常短,大致分 為:

- (1)Under Bump Metal (UBM)的金屬 濺鍍

- (2)黃光製程

- (3)電鍍製程

- (4)金屬蝕刻製程

- (5)熱處理。

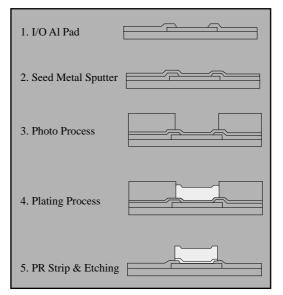

如圖四所示為標準的金凸塊製程流程,在這製程流程中,除了電鍍製程以外,均和薄膜製程相同的,以下是對各項製程作一簡單介紹。

#### 一.濺鍍製程 (Sputter)

濺鍍製程是以真空濺鍍的方式將 UBM濺鍍至晶圓表面上,此步驟的製程,在凸塊製程中是控制品質的第一步,因為UBM具有兩項功能:

(1)Diffusion Barrier

(2)Adhesion Layer。

濺鍍的品質直接影響產品的可靠度 , 各

個公司所使用的金凸塊UBM材料大致相同。大都是以TiW/Au為UBM及當作電鍍的導電層。製作方式是以真空濺鍍或是真空蒸鍍方式將TiW/Au膜鍍至晶圓上,作用之一的Diffusion Barrier是防止鋁和金的相互作用而破壞金屬層的結構,因為鋁和金可以形成很好的合金,但是合金的形成會造成鋁層的破壞,所以一層Diffusion Barrier 是要防止這兩金屬相互反應,UBM另外一項功能是當作接著層(Adhesion Layer)。凸塊是結合Inner Lead及IC 鋁墊的一個介質,而金和鋁墊的結合面是最脆弱的,所以中間的UBM就成為其接著介質以增強其機械強度。

#### 二.黃光製程

黃光製程是先在晶圓表面塗佈一層 光阻, 這光阻的厚度依凸塊的高度而 定,通常金凸塊的高度為12µm~25µm, 則光阻的厚度可控制在15μm~30μm,至 於使用正光阻或是負光阻則依各家製程 選擇而定。這需要配合電鍍液及其電鍍 條件,因為光阻製程之後是電鍍製程, 而光阻在電鍍液裡要非常穩定才有可能 完成電鍍製程。光阻塗佈烘乾之後則進 行曝光動作,曝完光顯影後的光阻,是 在晶圓上把需要電鍍區域的孔洞顯影並 開出來,其餘的區域還是由光阻覆蓋, 之後即可進行電鍍製程。厚光阻在半導 體製程中並不普遍,其材料供應商(如 表一所示) 並不多。或許可以考慮使用 在PCB製程上的乾膜,但是乾膜材料需 要進一步改良,達到IC等級的材料規 格。

曝光系統可用步進對準機(Step-per) 或是一般曝光機(Aligner),由於凸塊的規格大致在35μm以上,所以一般曝光機的對位系統皆可達到所要求的解析度。但IC的黃光製程所使用的設備幾乎是步進對準機,其中不同光學系統的銜接,則要靠IC廠和Bumping House之間的配合 ,互相傳輸光罩的圖檔,要不然

Bumping House在光罩及Bumping製程上的對位系統將會產生連接不匹配的問題

顯影的製程可分為兩種:

- (1)Immersion Type

- (2)Spray及Puddle

當然這兩種各有其優缺點如表二所示。選擇何種方式是以產品規格及價格二者為考量因素,若是在Large Bump Pitch則Immersion方式是快速及最直接的顯影方式,因為只要有良好的流體及溫度控制的化學槽皆可達到顯影的規格,而且是以一個Cassette的方式在顯影,所以在Throughput 及顯影液的使用量都是最經濟的,但是在Small Pitch及要比較高解析度的顯影規格,Spray及Puddle方式才有可能達到。LCD Driver IC 的 Bonding

圖四 標準的金凸塊製程流程

### 表一 適用Bumping製程的光阻種 類

| 產品型號   | 供應商     | 最高厚度/<br>Coating | 光阻型態 |

|--------|---------|------------------|------|

| AZ4602 | Hoechst | 10-20μm          | 正光阻  |

| AZPLP  | Hoechst | 10~20μm          | 正光阻  |

| THB-30 | JSR     | 15~30μm          | 負光阻  |

|        |         |                  |      |

Pad 和一般IC 不同點在於Pitch 和Size 的 規格都很小,一般IC Bonding Pad 的設計 都是以Wire Bonding 方式封裝為主,所以Pad Size 大多在50 μm 以上,再加上約 20 μm 的間距,但是LCD Driver IC 其主要封裝方式為TCP 及COG,所以其 Pad Size 有小至 40 μm,而間距有小至 10~15 μm 之間,若是沒有用Spray Type 的顯影方式是無法達到所需的解析度。

#### 三.金電鍍製程

電鍍製程是控制金凸塊品質的最重要項目之一,此製程系統總共分為三部份:

- (1)電鍍系統

- (2)電鍍液

- (3)晶圓夾具

- 以下則對此三項作一介紹:

- 1. 電鍍系統

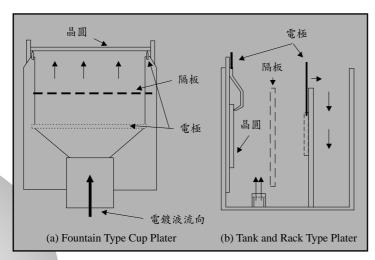

電鍍系統是指電鍍設備。在電鍍設備型態上也分為兩種,第一種是噴流式

圖五 (a)&(b)為兩種電鍍槽的設計模式

(Fountain Type)的此種電鍍系統如圖五 (a) 所示,晶圓是面朝下,而電鍍液是由下往上噴向晶圓的電極。而電極的接觸點則是在噴流口邊緣,電鍍液由下往上噴之後,再經由晶圓邊緣回流到過濾系統;第二種是一般的電鍍槽,它和PCB廠所使用的電鍍系統類似,如圖五 (b) 所示,兩個平面電極,中間為隔板,以及電鍍液的噴流系統,其構造簡單可隨著槽體擴大而增加產能。但是晶圓的製程傳輸系統完全和一般PCB不同,這一觀念是在製作晶圓所必須完全考慮的,表三所示為此二類電鍍系統的優缺點比較。

電鍍系統主要是構成電鍍的控制系統,其中包括電鍍的 Power Supply、液體流量控制、溫度控制、過濾系統等,因為在晶圓上的電化學反應及金屬的沉積,是經由電鍍系統的控制而得到所需的電鍍當量,而將所需的金屬沉積至所需的區域,這是在設計電鍍系統需要考慮的,再加上如何控制電流使其平均分佈在晶圓表面上,對產品良率都有很大影響。使用在晶圓上的電鍍設備,以目前來說,並不是很成熟而且很昂貴,所

#### 表二 為二種顯影方式的優缺點

|            | Immersion        | Spray puddle    |

|------------|------------------|-----------------|

| 設備         | Chemical Station | Developer Track |

| Throughput | 高                | 低               |

| 製程 Cost    | 低                | 高               |

| 顯影能力       | 只能做              | 可做              |

|            | Large Pitch      | Small Pitch     |

| 製程自動化程度    | 低                | 高               |

| <b>=</b> -      | 為兩種オ        | — IIII —   | ᅷᄉᅉᅪ      | 5 <del>6</del> 6 6 1 | L   |

|-----------------|-------------|------------|-----------|----------------------|-----|

| <del>75</del> — |             | \ I=I #! - | -/ 土庫 /庫  | 9 H'\   F            |     |

| 表二              | 一分回 에서 까무 기 | 10142      | レノ・・シマ イド | 4 U'I L              | d a |

|                          | 晶圓放置方式  | 晶圓傳輸  | 鍍液管理 | 晶背保護 | 設備價格 |

|--------------------------|---------|-------|------|------|------|

| 噴流式<br>(Fountain Type)   | 面下      | 可自動化  | 可    | 不需要  | 貴    |

| 上噴式電鍍槽<br>(Tank or Rack) | 和噴流方向平行 | 較難自動化 | 可    | 需要   | 便宜   |

以每家Bumping House 都有其獨特方式以 降低製程成本。而對台灣半導體設備廠 商來說,可以說是容易切入的一項新興 半導體設備,因為現在及未來銅製程在 半導體製程也是發展重點之一。銅製程 則會用到電鍍銅製程,所以晶圓的電鍍 設備對台灣的設備廠商來說,是很適合 投入研究開發的一項。若是晶圓的電鍍 設備成熟,不僅可以支援台灣Bumping的 產業,同時發展銅製程,而且在半導體 設備的產業上,亦可順勢佔一席之地。

#### 2.電鍍液

電鍍液是在電鍍系統中決定鍍金品 質的要素之一,每家電鍍液廠商都有其 獨特配方以滿足客戶品質需求。金的電 鍍液通常有兩類:

#### (1)氰酸類

#### (2)非氰酸類。

在環保比較嚴苛的國家,已漸漸禁止氰酸類電鍍液的使用,但是由於氰酸類電鍍液從以前的歷史經驗累積,通常都能達到較好的電鍍品質及較長的電鍍液使用壽命。電鍍液的成份很複雜,不同Supplier 有不同的配方,其所強調的項目如表四所示,但最終還是要以結果而定,所以選定電鍍液的供應商,需要有長時間的驗証規劃,當然最好是依照客戶的經驗來選是最直接,風險也是最低的。

電鍍液的管理在電鍍製程品質維護上亦是非常重要,因為在此電鍍過程中,控制因子有數十項,每一項幾乎都影響電鍍品質的持續性,如表五列出其中監控的項目,每項皆會影響電鍍的品質。當然若能整合成為完全由電腦系統監控則是最好方式,可以減少人為的錯誤,因為在電鍍製程管制上,人為操作錯誤還是佔最大比率。

#### 3.電鍍夾具

晶圓的電鍍夾治具設計亦是非常困 難的一項,因為晶圓的屬性是易碎,半

#### 表四 廠商提供的電鍍液規格

|               | Company A                       | Company B | Company C                       |

|---------------|---------------------------------|-----------|---------------------------------|

| 金屬濃度g/1       | 10~14                           | 7~10      | 8~12                            |

| 析出純度          | 99.99+                          | 99.99+    | 99.99+                          |

| 硬度(Hv)        | 60~90                           | 80~110    | 80~110                          |

| 析出重量mg/µm cm² | 1.92                            | N/A       | NA                              |

| 析出速度min/μm    | 3.2 min<br>0.5A/dm <sup>2</sup> | N/A       | 4.1 min<br>0.5A/dm <sup>2</sup> |

| 析出效率mg/A.min  | 110 120                         | 115 120   | NA                              |

| 電流密度A/dm²     | 0.1~1.2                         | 0.2~1.0   | 0.4~0.8                         |

| рН            | 7.6~7.8                         | 6.0~6.8   | 7.5~7.8                         |

| 操作溫度℃         | 60~70                           | 60~70     | 55~65                           |

# 表五 影響電鍍品質的要素及其管制方式

| 項目    | 分析方式                  | Contorl Method |

|-------|-----------------------|----------------|

| Au濃度  | ICP                   | SPC            |

| рН    | pH meter              | SPC            |

| 温度    | 溫度計                   | SPC            |

| 金屬不純物 | AA                    | SPC            |

| 有機不純物 | UV                    | SPC            |

| 比重    | 比重計                   | SPC            |

| 電流條件  | Current Control Meter | Monitor        |

導體表面不能觸碰,這都使夾治具在設計上受到很大的侷限,由於夾治具設計的困難度高,所以每家廠商都視為Know-How而不輕易示人,因此各家廠商都可發揮其想像力,發展出自己獨特的電鍍夾治具。

#### 四.光阻去除及金屬蝕刻製程

触刻製程是在光阻去除後段,將 Sputter的Au及TiW蝕刻去除,蝕刻Au及 TiW是在製程中較易達成的項目。在製 程中主要控制的項目是

#### (1) Undercut

#### (2)金屬殘留(Residue)

Undercut是過度蝕刻所造成的,而 金屬殘留則是蝕刻不完全所造成。當然 Undercut及金屬殘留最終都會影響到可 靠度,所以在製程管制上也是不可忽視

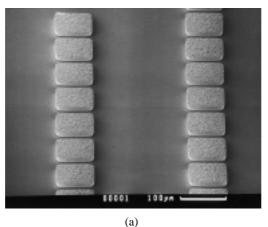

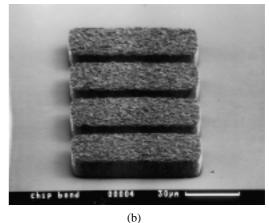

圖六 (a)&(b): 金凸塊的SEM照片

# 表六 適用於TCP及COG金凸塊的品 質項目規格

| 項目                     | 規格           | 應     | 用                                       |

|------------------------|--------------|-------|-----------------------------------------|

| 投口                     | <i>አ</i> ቲ1ロ | TCP   | COG                                     |

| Au硬度<br>(Vickers)      | 30-80 Hv     | 適用    | 適用                                      |

| 表面粗造度                  | <3.0 μm      | 適用    | 適用                                      |

| 剪應力(shear<br>Strength) | ≥4g/mil²     | 適用    | 適用                                      |

| 高度                     | 12-20μm      | 適用    | 適用                                      |

| 平整度                    | <2.5μm       | 適用    | 適用                                      |

| 面積                     | 依設計而定        | 依設計而定 | 23000 μm <sup>2</sup><br>(依ACF<br>種類而定) |

的項目。

# 金凸塊的品質要求

金凸塊的成品如圖六所示,但是實 際凸塊產品在凸塊周圍會隆起,這是由 Passivation高度造成的。品質及規格項 目如表六所示,是適用一般的金凸塊產 品製程,但若有其他的特殊規格可以修 改製程及設計訂出特殊規格。這些品質 規格只是針對外觀及機械特性,在製程 上可以訂出管制規格,但內在的品質如 金凸塊的晶體結構, Contact Resistance 及UBM的可靠度,無法訂出製程管制的 規格,只能作製程監控或長期分析。

### 結語

凸塊技術只是元件結合的起始點, 未來在元件結合上是否會發展另外一項 結合技術,則不得而知。但是由目前凸 塊技術而衍生出來的元件封裝技術則會 愈來愈多,例如TCP、COG、COF、FC 等或是3D以及其它微機電系統(MEMS) 都會用到凸塊技術。在臺灣半導體產業 愈來愈成熟的環境下,所衍生的半導體 產品種類也會愈來愈複雜,各種產品的 屬性會衍生出不同的封裝技術,但是其 元件結合則會大同小異。所以凸塊技術 將是封裝技術的一個基礎,而且其掌控 IC訊號的進出,凸塊製造技術的發展, 會將IC的封裝技術帶進另一個層次。

# 參考文獻

- (1) 火田 田賢造: TAB 技術入門 (1990)

- (2) Wafer Bumping Technology, 山本好明, 電子材 料, 5, 1999.

- (3) Metallization Scheme Providing Adhesion and Barrier Properties, US Patent :4,927,505.

- (4) Method of Manufacturing a Bump Electrode, US Patent:5,310,699