# 先進構裝-3D堆疊構裝技術簡介

#### 彭逸軒

工研院電子所先進構裝技術中心 構裝製程技術組 副工程師

#### 摘 要

隨著溦機電加工技術的成熟發展,已可以預期到溦機電技術在未來生活中將扮演相當重要的 角色,而構裝技術之演進已從二維平面進展至三維立體構裝(3D Package),由此技術開發之 產品具有高效能、高密度及小尺寸等特性,同時能將Logic、Memory、RF與Passive等元件 整合成溦小系統,更甚者,它能依各種型態之可攜性產品的需求做系統整合。

#### 關鍵詞

3D堆疊構裝(3D Stacking Package); 晶圓級構裝(Wafer Level Package); 晶圓簿化(Wafer Thinning); 系統整合式構裝(System on Chip, SOP)

## 前言

行動式通訊電子產品的需求量與日 遽增,在這些產品的消費刺激下,要求 高功能多元化的電子產品,如高速、高 容量及輕薄短小,已經是無可避免的趨 勢,同時由於使用者的要求,驅動產品 製程亦一次又一次的革新及進步中。

現今許多電子產品中都用到高密度 積體電路的封裝,如大哥大手機、 PDA、攜帶式電子系統、人造衛星、軍 用航空電子及其他手提式系統等。幸運 的是,現有成熟的深次微米積體電路製 作技術,可使系統設計者有能力達成整 合系統在一晶片上(System on Chip; SoC) 的任務。然而SoC仍有一些困難點存在, 例如電性特性訊號延遲及雜訊,或者由 於次系統積體電路製程造成半導體製程 的不相容性。

近來由於電子產品構裝及半導體製程走入微小化,使得傳統平面構裝面臨嚴重的考驗,再加上多媒體資訊時代的來臨,資訊的傳輸容量及速度要求都更為提高。然而資料以高速大容量及高頻處理時,訊號接點會發生失真、延遲及電力消耗等問題,因此在解決上述困擾之同時,加上產品輕薄短小趨勢,推動了3D構裝時代的來臨。

## 3D構裝的特色

近年來發展的先進封裝技術如3D堆 疊、多晶片模組(MCM)及MCM的3D堆疊 封裝形式, 使系統無論在質量、體積及 電力功率消耗都大幅縮小。3D接合技術 多採垂直式接合,使多層晶片能夠形成 堆疊, 對高度連結晶片的要求是一大好 消息。換句話說,晶片可擁有較多的輸 入/輸出(I/O)接腳或接點,同時垂直式的 連結方式大幅縮小訊號接點的間距。二 維及三維(以下簡稱2D及3D) 堆疊是以 新的薄化技術(Thinning)、承接(Handling) 及製作包含被動元件的基板來達成。

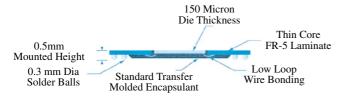

新的薄化技術允許晶片厚度薄至 10μm, 且沒有損及晶片的功能。此項技 術最主要的優點在於薄膜製程可被執行 在晶圓級的製程上,而不需藉由覆晶或 打線技術。圖一所示為超薄晶圓堆疊。

3D技術建立於堆疊任何元件的基礎 上,舉例:記憶體、微處理器、感測器 及促動器等,而這些元件的封裝又包含 裸晶、塑膠封裝、TSOP、PQFP及BGA 等。3D模組可用表面黏著方式(如:I型 腳、鷗翼腳Gull Wing或BGA) 組裝於基 板上,或藉由密封的陶瓷封裝整合2~4個 元件在内(如記憶電容等)。

3D構裝的趨勢及應用,使封裝朝向 立體結構(晶片堆疊及封裝堆疊)及超 薄封裝技術發展,焦點將放在無線手機 相關的趨勢及應用上,它同時要求較高

等級的效率,以降低尺寸、重量及成 本,達到更多的特色、功能及服務。圖 二為一多晶片模組構裝之記憶體。

## 3D構裝的結構分類

堆疊型晶片級尺寸構裝(以下簡稱 S-CSP) 技術的進步,尤其以超薄封裝及 晶圓級封裝技術為產品主要創新的促成 因素。3D堆疊型態之主客觀條件因人而 異,其結構分類並無共通之標準,依據 文獻,大致將其歸類成三大類以利討 論。以下將陸續討論個別堆疊型態之結 構、應用及電性效益。

#### 一、封裝級3D構裝

封裝級構裝(Package Level Stacking) 是以先行封裝好的元件,將之以3D構裝 的方式或概念堆疊組裝起來,它的訊號 連接需藉由封裝體外部四周邊緣構成焊 接腳,使其他封裝體堆疊相連後,可以 邊緣導體焊接形成上下晶片的接合,例 如在封裝體邊緣構成引腳,引腳與引腳 間以銲錫焊接在一起(如圖三)。另外也 有以陣列銲錫凸塊作為接角連結。好處 是此種構裝形式簡單、製程成本低,且 可對先行封好的元件進行測試,因此良 率較高;但由於訊號導線較長,速度無 法提升太高。

封裝級的3D構裝大部分採以薄型軟 式基板為載體,目的在減小構裝體完成

'圖三 應用在 SRAM、DDR及 PC133等記憶體 之3D PCB組裝結 構 (Source: Canopy<sup>TM</sup>)

▲圖一 超薄晶圓堆 疊(矽晶圓)

◀圖二 多晶片 模組一Cluster-II 號太空船上固態 記錄器的640Mb 記憶模組(資料 來源: 3DPlus Electronics)

後的厚度、高度及重量,如圖四Amkor公司的 etCSP堆疊元件即是。另外也有將載體以直立形式作為元件連接的構裝形式,如圖五所示。

#### 二、晶片級3D構裝

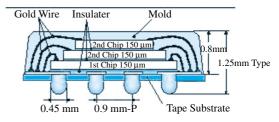

晶片級堆疊構裝(Chip Level Stacking)方式是以尚未封裝成形的裸晶(Bare Die),直接以3D方式將晶片置於晶片上進行堆疊,所以也可稱為Chip on Chip。它是以裸晶片黏著或相互貼合堆疊積層,而所使用的訊號連結方式主要以打線(Wire Bond)或覆晶(Flip Chip)等方法連結到承載的晶片或基板上。這種堆疊構裝早先是由Sharp公司及Amkor公司合作開發出來的,其基本結構如圖六所示,基本上每一堆疊層的晶片尺寸大小是由下往上遞減的,因此打線仍可由晶片周圍的配墊拉至基板。圖七所示為Intel公司所做的Wire Bond 3D構裝實體,

直接積層IC再以打線方式做電性訊號連結,大部分Chip on Chip的3D構裝都是採用這樣的技術,它的連接導線較封裝級堆疊短,可預期電性較佳,組裝完成後可得到更薄的元件。

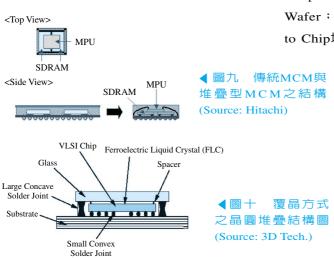

然而當堆疊的晶片大小相同,又必須以打線方式接合時,有人便想出在晶片間加入中介層,以增加空間方便打線,例如圖八便為Amkor公司之相同尺寸CSP堆疊封裝。晶片級堆疊構裝的型態,其實可視為多晶片模組(Multi Chip Module, MCM)的延伸,許多多晶片模組的概念可直接應用於3D模組的構裝,最重要的觀念即是整合不同製程晶片於同一模組,如圖九所示,將晶片接合的方式由2D改為3D堆疊結構,如此不但可大幅縮小構裝面積,更是製程邁入系統整合(System in Package; SiP)的一重要里程碑。

另外一型3D晶片堆疊使用覆晶接合 方式組裝,圖十所示為其簡單之結構示

▲圖四 etCSP薄板封裝剖面結構圖(Source: Amkor Co.)

▲圖六 打線連接之晶片堆疊結構 (Source: Amkor&Sharp Co.)

▲圖五 封裝級堆疊構裝

▲圖七 打線連接之晶片堆疊 (Source: Intel Co.)

▲圖八 相同尺寸CSP堆疊封裝(Source:Amkor)

輯

意圖,此種方式涉及IC 設計的重新配線。覆晶堆疊的優勢幾乎可以在不變更原晶片IC設計下進行,目前大部分晶片的焊墊呈Peripheral或陣列式排列,且由於晶片間連接的導通孔尺寸較大,銲錫凸塊的形成與後段製程幾乎可在不改變現有之技術下完成,但扼腕的是由於其導通孔的尺寸較大,只能以Peripheral排列,若想以陣列排列,將縮減可製造電晶體的區域,因此,其I/O接腳數將無法有效的提昇。

#### 三、晶圓級3D構裝

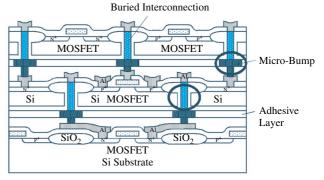

晶圓級堆疊(Wafer Level Stacking)又可稱為Wafer on Wafer垂直積層的構裝方式,此種方式利用到前述提及的電路重佈技術(Redistribution),來達到上下晶圓對晶圓的電路導通。與直接晶片堆疊的目的相同,直接堆疊晶圓可以達到最短的訊號導通,提升電氣特性。

3D晶圓堆疊大致又可分為兩大類型,一為直接晶圓堆疊的立體構裝,此技術是以蝕刻方式在晶圓上製作出導通穿孔,接著再製作形成晶圓間相互導通之電極凸塊,之後以相互對位堆疊的方

式進行組裝,其結構示意圖如圖十一所示,此製程為先進的構裝方式,利用現有半導體製程以及晶圓薄化技術,能夠做到高組裝密度及較佳的電氣特性,惟此部分尚有些關鍵技術仍未成熟,量產尚有待評估。投入此部分技術研究的有日本Tru-Si科技、ASET科技及日本東北大學。

另一種為在IC半導體製程時就一併製作好線路重佈與埋孔,同時以半導體製程進行堆疊,必須在組裝前就先設計好所有的埋線、導通孔及IC佈線,優點是此種方式能夠得到最大的構裝密度及有效利用晶片面積。以Irvine Sensors科技所發表3D堆疊結構為例,在晶圓製作時就已經將導通的電極預先做好,並導引到晶片的側壁,與導通孔在晶片内部的設計比較,將訊號連接線佈局在堆疊晶片外圍的結構,此法除可保全IC設計的佈局,亦可有效利用晶片面積。Irvine Sensors的3D堆疊構裝技術已應用在DRAM及快閃記憶體模組等軍事及太空產品上,圖十二所示為其結構與實體。

以產量的角度來看,Wafer to Wafer 堆疊可一次完成較多的單位,而Chip to Chip的單位時間產量則遠少於Wafer to Wafer:但以良率的角度而言,則是Chip to Chip堆疊位居優勢,因為KGD(Known

▼圖十一 3 D LSI結構剖面圖 (Source: Tohoku university.)

Good Die)之因素,Wafer to Wafer堆疊的良率會有累積加乘,如果單層的良率為80%,堆疊三層時其良率將下降至0.8³=51.2%,最嚴重的情形可能會因為其中某堆疊層損壞而造成整個單位的堆疊失效,這將是晶圓堆疊所面臨之一大挑戰,也是3D構裝形式中最複雜也最先進的構裝方式。此技術尚需克服的因素甚多,因此要臻至成熟階段仍需一段努力開發,需整合前段IC設計者與後段組裝業製程的能力方可實現,同時一併考慮成本因素也是走入量產的一大門檻。

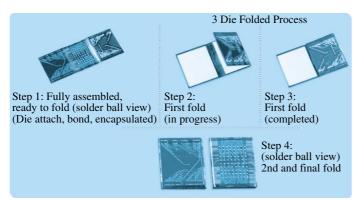

其他的特殊堆疊結構,如圖十三所示Tessera公司的專利開發,以軟板當作承載體及電路配線,以折疊堆疊的方式構成3D立體構裝。圖十四為Irvine Sensor科技研發的16Mb 25µm超薄晶圓快閃記憶體,晶圓黏貼於軟板上,組裝後彎曲半徑每微米厚度可達1mm。3D堆疊構裝

(a) CHIP STACK ENABLES 3-D INTERCONNECT

Packaging technique bumps circuit density

Ceramic substrate

(metalized on

both sides with

through holes)

Bus metal

(two sides)

Blank ceramic substrate

▲圖十二 3D直接晶片堆疊之(a)側壁導線結構與(b)實體 (Source: Irvine Tech.)

▲圖十三 折疊式軟板堆疊3D構裝製程(Source: Tessera Tech.)

受限於專利的情形其實甚多,因此各廠家在開發新構裝結構上,無不絞盡腦汁推陳出新,在此僅略作介紹不深入討論。

## 3D堆疊構裝技術的優點

- 1. 輕薄短小是3D堆疊技術最大的優勢,尤其在可攜式的通訊用電子產品。

- 2. 封裝效率大幅提昇。一般封裝效率定義為晶片與封裝腳位(Footprint)的面積比例,傳統平面式構裝因晶片面積永遠小於封裝腳位面積,所以封裝效率一定小於100%,而3D構裝因堆疊的關係,封裝效率會大於100%。

- 3. 訊號延遲(Delay)指的是在電子系統中,在線路高速中的訊號會因傳達行經不同界面接合點或路徑長短,而造成總體的傳遞訊號延遲,通常路徑越長越嚴重。3D堆疊構裝正好縮短了界面的路徑,同時大幅降低寄生電容及電感的效益。

- 4. 雜訊(Noise)降低,雜訊通常定義 為加在一般有用的訊號中,不希望得到 的訊號,在一個高效率的系統中雜訊是 很嚴重的問題。雜訊的來源通常包括反 射(Reflection)、串音(Crosstalk)、切換 (Switching)及電磁干擾(EMI),會降低 Edge Rate、減少雜訊裕度(Noise Margin) 和引起邏輯切換錯誤等,導致系統效能 不佳。與訊號延遲問題相同,當界面接 合路徑越短,會產生雜訊的機率就越

▲圖十四 25µm超薄16Mb快閃記憶體晶圓構裝 (Source: Irvine Sensor Tech.)

低。

5. 電力功率損耗,因為P=fCV²,其中 f為頻率,C為電容,V為訊號路徑之跨壓。因此若不考慮環境條件之頻率與跨壓,在一電子系統中電力消耗取決於接合點或路徑的寄生電容,而寄生電容又直接正比於訊號路徑的長度,故3D堆疊能降低電力功率損耗。

6. 頻寬瓶頸,通常電子通訊系統的 效能瓶頸受限於界面接合的頻寬,尤其 是在記憶體元件中,在這些元件中能控 制低訊號延遲及高匯流排(Bus)寬是最好 的,若以3D堆疊構裝來整合記憶體及 CPU元件,必能解決而獲取較大的頻 寬。

# 3D堆疊構裝技術面臨的瓶 頸

在商品市場化之前都必須考量3D堆 疊構裝的可靠度,最令人詬病的是熱傳 問題,一完整的熱傳課題包括:1.熱傳 導,2.熱應力。3D堆疊構裝一向在熱傳 的表現上較差,因此目前來說,大多應 用在記憶體堆疊上,因為記憶體功能操 作所產生的熱遠比邏輯運算所產生的熱 小許多,以目前記憶體堆疊的產品而 言,其所面臨的熱傳問題幾乎可以省 略,但未來如要應用於較高階產品時, 本問題將面臨極大的挑戰。另一方面, 伴隨而來的是熱應力問題,其來源仍是 材料與材料間熱膨脹係數(CTE)不匹配所 致,加上晶片薄化後導入金屬層應力, 堆層結構造成應力分佈越趨複雜,相信 對產品的可靠度有極大的負面影響。

還有一項3D堆疊構裝所面臨的問題,在於傳統或現有的設計軟體或工具如CAD,根本無法處理3D的設計法則,

而開發中的設計者以自行的設計工具處理製程需求條件,而3D封裝形式設計複雜尚無定則,更增加了堆疊構裝的設計、製程及測試成本。另外,例如晶圓導通穿孔技術、Wafer薄化技術及堆疊精密對位誤差±2µm内,這些技術雖然不是瓶頸,但卻是製程上的關鍵,尚待致力於技術的成熟化。

### 結語

在Moore's Law的極限即將來臨下,半導體微細化的製程技術已屆臨技術邊緣,3D堆疊構裝有其投入研究開發之趨勢及必要,且技術進入障礙較小。無論是多晶模組堆疊或晶圓堆疊,在終極目標System on Chip出現之前,趨勢將是朝向System in Package發展與努力。

另外一個努力的目標是如何將不同 材料的IC元件堆疊在一起,這也是未來 的技術發展趨勢,同時也可能帶來新一 波的產業革新。

# 参考資料

- Morihiro Kada, Lee Smith, Pan Pacific Microelectronics Symposium conference, 2000.

- 2. F. Al-sarawi, D. Abott and D. Franzon, IEEE trans. on components package and manufacturing tech., part B, vol.21, no.1, 1998.

- 3. H. S. Ko, J.S. Kim, et al., IEEE transactions on advanced packaging, vol. 23, no. 2, 2000, p.252

- 4. Y. Tomita, T. morifuji, et al., Elec. Comp. Tech.

- 5. D. Bollmann, R. Braun, et al., Materials for Advanced Metallization, 1997, p.94

- Amkor Technology Incorporation., "http:// www.amkor.com/".

- France 3D Plus technology, "http://www.3dplus.com/".

- 8. 金進興,工業材料雜誌,170期,p.100。